Systementwicklung Teil 2: SoCs für Debugging-Fähigkeiten entwickeln

Anbieter zum Thema

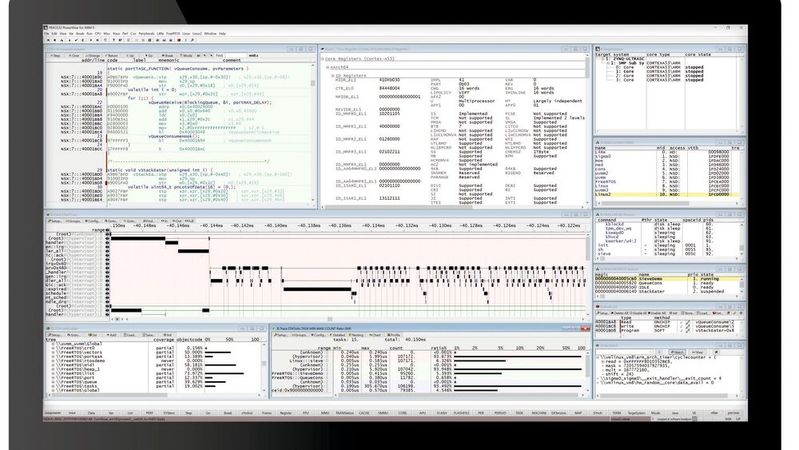

In Teil 1 wurde die Bedeutung von Debugging und Tracing bei der Entwicklung von SoCs diskutiert. In Teil 2 geht es um Sicherheitsaspekte, Off-Chip-Trace-Funktionen und die wichtigsten IP-Blöcke für eine leistungsstarke Debug-Infrastruktur.

Ein aus Debugger-Sicht optimal gestalteter Chip bedeutet für den Kunden weniger Aufwand, eine schnellere Markteinführung und vor allem geringere Entwicklungskosten sowie für den Chip-Hersteller einen höheren Absatz, denn jedes fehlgeschlagene Projekt führt zu reduzierten Stückzahlen. In Teil 1 dieses Artikels wurde die Bedeutung von Debugging und Tracing für Time-to-Market diskutiert und erste wichtige Überlegungen für Debug-freundliche SoC-Designs angestellt. An dieser Stelle knüpft Teil 2 mit weiteren Punkten an.

Überlegungen für Debug-freundliche SoCs

Security: Die Implementierung von Sicherheitsmechanismen auf einem SoC ist für die Hersteller von entscheidender Bedeutung. Der Hersteller muss sich Gedanken über Bedrohungen und verschiedene Benutzertypen machen, welche Domänen für Debugging offen und welche gesperrt sein sollten und ob es zwischen ihnen Wechselwirkungen gibt. Auch die Signale für Reset und Power Down müssen im SoC getrennt werden. Debugging-Mechanismen bieten tiefen Zugriff auf interne Hardwareressourcen, was potenziell ein Einfallstor für Angreifer darstellt. Entwickler müssen daher Debugging-Schnittstellen standardmäßig deaktivieren oder durch Authentifizierung absichern. Nur autorisierte Benutzer sollten über diese Schnittstellen auf das System zugreifen können.

Melden Sie sich an oder registrieren Sie sich und lesen Sie weiter

Um diesen Artikel vollständig lesen zu können, müssen Sie registriert sein. Die kostenlose Registrierung bietet Ihnen Zugang zu exklusiven Fachinformationen.

Sie haben bereits ein Konto? Hier einloggen

:quality(80)/p7i.vogel.de/wcms/e3/25/e32569c8b06d7b5a20615f91859eb967/0130200276v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/af/9d/af9df19143eef8cdaa939072506b0410/0130190866v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/36/1e/361e1108cf35c2a5615ab8e039279671/0130152941v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ee/3d/ee3dda4ac1ebdc7b2d2c3895b98688f5/0130128194v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/80/df/80dfa5e9f86078d2716efda3572adc41/0129848633v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/11/ec/11ec13c15a411dbb10167f16ec03fdda/0125403466v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e2/37/e2375122003e64ae09cca191af0fcd07/0130120007v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/4c/b44cd7e6f97accbf06403023006ff56b/0127607345v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/1d/07/1d0774a54ae3261b3b2e757e470f7eed/0130073373v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/26/27/2627b8e236fad5d852b30f9ac7fe7afa/0129476624v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/6f/cd/6fcd73203044674045232a3c61d3d5b3/0128978470v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/c9/5d/c95d6a9a8190075acabe50d5bd5a1ec2/0128238623v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/66/b0/66b0f997f20340c96ac0227e5e8ed254/0130125154v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/f9/04f9fe79751531ea1fa9503e4bb9aece/0130106888v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/3d/56/3d561af57bf5f845debcb113fb3bf028/0130132304v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e1/24/e1240e6af098b7032beb54fd51576d78/0130139770v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/5b/15/5b15b693a9fe2b75aaa01d63077c0b80/0130091433v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/5d/82/5d8293b844665ec9043d2aa90dea976b/0129336773v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/aa/4b/aa4b45bdcdfb92a49821da177e24c8c0/0130115952v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2b/1e/2b1e8d874349b16c8a62742e0aa30678/0128885112v1.jpeg)

:fill(fff,0)/images.vogel.de/vogelonline/companyimg/76800/76895/65.jpg)

:fill(fff,0)/p7i.vogel.de/companies/69/8a/698aec7a30185/member-of-meister-group-logo-hohe-qualit--t.png)

:quality(80)/p7i.vogel.de/wcms/1d/37/1d37e437dbb4e4072304eaea41671216/0129249168v2.jpeg)

:quality(80)/p7i.vogel.de/wcms/46/ca/46ca78516796642321273b2547e4dd69/0128898902v4.jpeg)